製品・技術 2025.12.12

高速・高精度技術で多様な基板検査に対応 フライングプローブテスタ FA1815-01/-11 受注開始

フライングプローブテスタ FA1815-01

フライングプローブテスタ FA1815-01

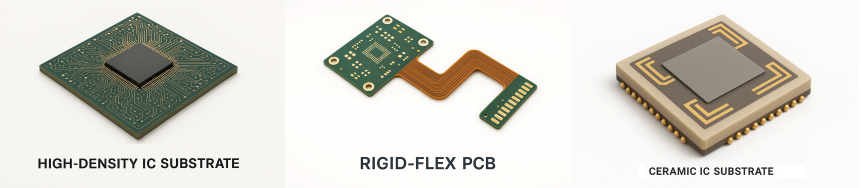

HIOKI(日置電機株式会社:長野県上田市、代表取締役社長:岡澤尊宏)は、2025年12月12日、フライングプローブテスタ「FA1815-01」「FA1815-11」の受注を開始しました。FA1815-01/-11は、高密度多層基板やセラミック基板から高密度ICパッケージ基板*1まで、幅広い基板に対応した製品です。発売は2026年4月を予定しています。独自の技術を搭載したFA1815-01/-11は、従来機を上回る高速かつ高精度なプロービングを実現。これにより、スピード、精度、コスト効率といったお客様の主要な課題を解決します。本機は、開発から製造まで、あらゆる段階で高い歩留まりと長期にわたる信頼性を確保し、生産性を大幅に向上させます。

開発の背景

電子機器の進化に伴い、ICパッケージ基板の高密度化が急速に進んでいます。しかし、従来のジグ式検査機は、高密度基板の検査ニーズに対して技術面・コスト面ともに対応が難しくなっています。また、注目されているフライングプローブテスタにも、「高速に検査できるが、プロービング精度が低い」「プロービング精度は高いが、検査に時間がかかる」という性能上のトレードオフが存在していました。さらに、プロービング精度が高い装置や多数の検査ヘッドを搭載した高速検査装置は、導入コストが課題となっています。

当社は市場のこうした課題を踏まえ、プロービング精度と検査速度を最適化し、コストパフォーマンスに優れたフライングプローブテスタ「FA1815-01」および「FA1815-11」を新たに開発しました。FA1815シリーズは、多様化する検査ニーズに対応し、検査効率の向上とコスト削減に貢献します。

多様な基板に対応

多様な基板に対応

主な特徴

1. 向上したプロービング精度と最大100ポイント/秒の高速検査

正確なプロービングと検査ヘッドの高速移動を両立するには、機械の振動や外部環境による影響を最小限に抑えなければなりません。FA1815シリーズは、新たに設計した高剛性フレームと最新のモーター制御技術を採用しました。これにより振動や外部環境からの影響を最小限に抑え、高速移動においても高精度なプロービングを実現します。

2. 測定対象にやさしい10V/100GΩの低電圧絶縁抵抗試験

誤動作や故障につながる潜在的な欠陥の検出には、絶縁抵抗検査が効果的です。しかし検査時に高電圧を印加することで、測定対象のデリケートな回路を損傷するリスクがありました。そこでFA1815シリーズは、当社がこれまで培ってきた微小電流測定技術を駆使し、わずか10 Vの印加で最大100 GΩの絶縁抵抗検査を可能にしました。

3. 多様な基板検査を可能にする、静電容量測定と部品内蔵基板検査機能

FA1815シリーズは、HIOKI独自の静電容量測定方式による高速検査や、インサーキットテスタの技術を応用した部品内蔵基板検査機能により、幅広いアプリケーションを実現します。数十年にわたる計測器のノウハウをもとに、高精度で信頼性の高い測定ソリューションを提供します。

主な用途

- FCBGA*2 タイプICパッケージ基板の導通・絶縁・配線抵抗検査

- シリコンブリッジ*3付きハイブリッド基板の電気試験

- 2.5次元/3次元ICチップレット*4のRDL*5試作品・開発品の品質検査

- 5GおよびIoT半導体デバイス用高密度基板の検査

- スマートフォン、ウェアラブル端末、自動運転車など高性能製品向け基板の検査

製品ラインアップ

- フライングプローブテスタ FA1815-01 水平両面オフラインタイプ

- フライングプローブテスタ FA1815-11 水平両面インラインタイプ

受注開始日

2025年12月12日

製品発売日

2026年4月

注釈

- *1:ICパッケージ基板: 半導体チップとプリント基板の間に使用され、電気信号や電力を伝送するための多層中間基板。インターポーザを含む。

- *2:FCBGA: Flip Chip Ball Grid Arrayの略で、チップをフリップチップ実装し、基板裏面のはんだボールで接続した高密度パッケージのこと。放熱性に優れている。

- *3:シリコンブリッジ: 極微細端子を持つシリコンインターポーザの一種。狭ピッチでのマルチチップ接続を可能にし、基板面積を削減しながら信号速度を向上させる。

- *4:2.5D/3D ICチップレット: ダイを積層または半積層状態で近接配置・相互接続することで、小型・高密度・高速・低消費電力のICパッケージ基板を実現する技術。

- *5:RDL: Redistribution Layerの略。ICパッケージ基板上のチップを再配線し、高密度化・多層化・微細化を実現する配線層。

本件に関するお問い合わせ先

日置電機株式会社 テストシステム部

- 記載されている情報は本文章発行日現在のものです。

- 予告なしに価格、仕様、そのほか本文章に記載の情報は変更になる場合がありますので、ご了承ください。

- 本文章で使用している会社名および製品名は、各社の登録商標もしくは商標です。