JTAGテストと疑似接触検査で最強(*1)の接続信頼性保証

疑似接触まで検出できるHIOKI独自のリード浮き検査方式と、リードレス部品に対しても高いテストカバレッジを誇るJTAGテストの組み合わせで、高次元の接続信頼性を高効率で得られます。

(*1電子回路基板の実装後検査に於いて、通電検査による半田付け接続信頼性検査で検出可能な不良内容とそれに要する時間やコストなどを比較した場合に対する当社の見解です。全ての観点を総合したものではありません。)

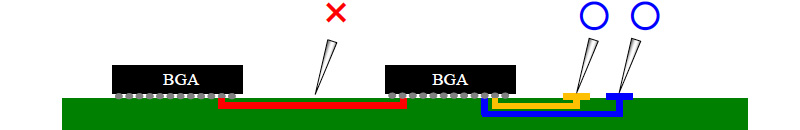

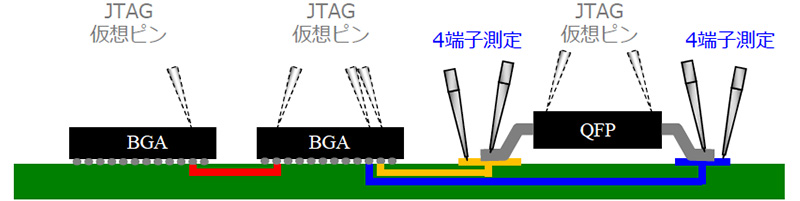

HIOKIフライングプローブテスタ独自のリード浮き検査技術を使って、プローブ接触できる端子は、電気的属性を問わず全ての端子でプアソルダー/プアコンタクトといった疑似接触を含む高い次元の半田付け保証を行い、BGA/QFNなど直接プローブ接触できない端子は、通電検査で高いテストカバレッジを誇るJTAGテストシステムで接続保証する。この組み合わせで検査の効率と品質を高次元で両立させることができます。

加速する部品の小型化や高集積化で、テストカバレッジの低下にお困りではありませんか?

- SMTコネクタが増え、導通以上の高次元半田付け接続信頼性を要求されている。

- 輸送中の振動や経年で顕在化する疑似接触や半田クラックまで保証したいがX線はどうも…

- 4端子足浮き検査方式でプローブ接触ができないリードレス部品などの保証はどうする?

- 増えるBGA/QFN部品。BGA-BGA間の接続保証はJTAGテストが最も効率的。

バウンダリスキャンテストの必要性

部品の小型化、高密度実装化に伴い、基板実装現場では新たな課題が生まれています。

多用されるようになったBGAやQFN/SONなどのリードレス部品やSMTコネクタなど、外観上電極端子が見えない・触れない部品が多くなり、半田付け品質の保証が難しくなっています。

さらにBGAの狭ピッチ化も進んでおり、一般的にボールピッチが0.5mmを切ると実装不良が急増するとの情報が多く寄せられています。コスト面・品質面から見て、見えない・触れない端子の保証をどのように行うことが望ましいのでしょうか。

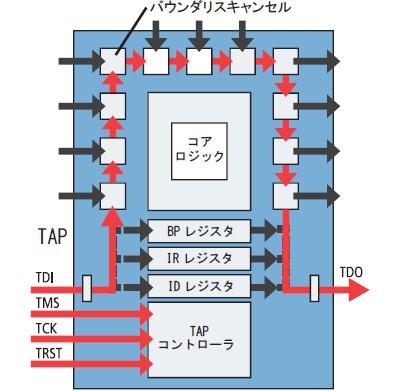

バウンダリスキャンアーキテクチャ

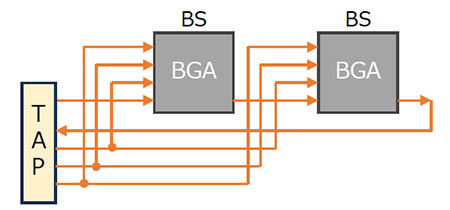

バウンダリスキャン(JTAG)は、プローブピンコンタクトが困難になりつつあった高密度実装基板に対する電気検査の方法として1990年にIEEE Std.1149.1として誕生した実装基板検査規格です。バウンダリスキャン対応デバイスに内蔵されたTAPコントローラを介して各テストセル(仮想ピン)同士の接続確認や簡単な動作確認を行うことができます。対応デバイス間をシリアル通信で結ぶ(ディジーチェーン)ことで、最低5本の信号線で試験が可能です。

これによりテストフィクスチャの物理的ピン数を大幅に削減することができる他、直接端子を見る触ることなく電気的な試験が可能となり、リードレス部品のテスタビリティを大幅に向上させることができます。

JTAGハイブリッド検査

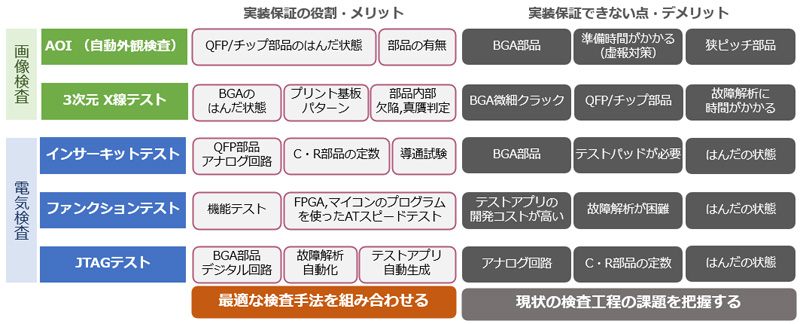

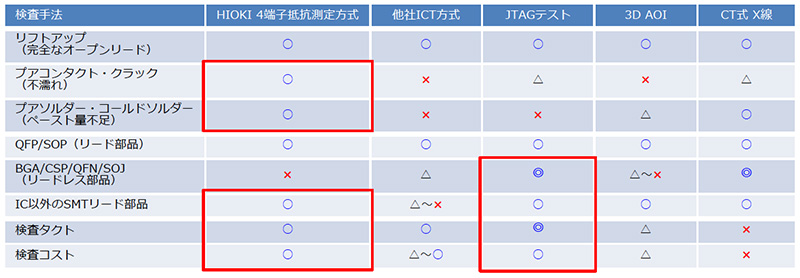

JTAGテストも含め、1つの検査手法で全てを網羅することはできません。

JTAGテストと従来の検査手法を目的に合わせて効率的に組み合わせて使用する「ハイブリッド検査」が効果的です。JTAGテストとインサーキットテストは同じ通電試験ですが、それぞれ異なる特徴を持っており、それぞれの特徴を活かした使い方をすることで、お互いを補完しつつ、効率良く高いテストカバレッジを実現することができます。

求められる品質をムリ・ムラ・ムダの無い検査手法を組み合わせることが重要

主なJTAGテストの内容(JTAG Technoligies社 JTAG ProVision)

(1) インフラストラクチャーテスト

TAPの5本の信号が正常にデバイスに接続されているかを確認するテスト

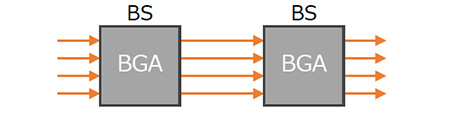

(2) インターコネクトテスト

バウンダリスキャンデバイス間の結線テスト

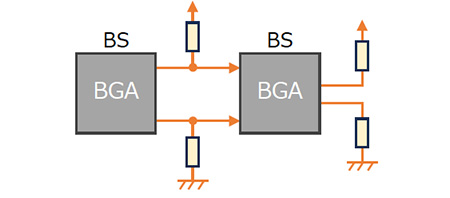

(3) プルアップ・プルダウンテスト

バウンダリスキャンデバイスと接続されているプルアップ抵抗やプルダウン抵抗の実装確認テスト

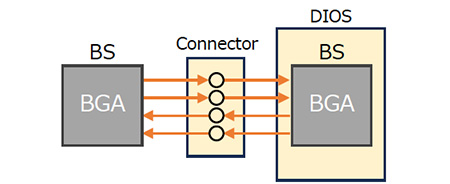

(4) コネクタテスト

バウンダリスキャンデバイスとコネクタ間のテスト。コネクタ外部にバウンダリスキャンが搭載されたI/Oアクセサリ(DIOS: Digital I/O Scanmodule)を接続してテスト

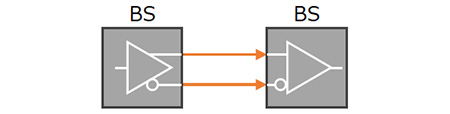

(5) Dot6テスト

IEEE std1149.6規格に準拠したAC結合や差動の結線テスト

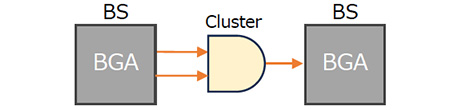

(6) クラスタテスト

バウンダリスキャン非対応デバイス(クラスタ)を動作させることで結線をテスト

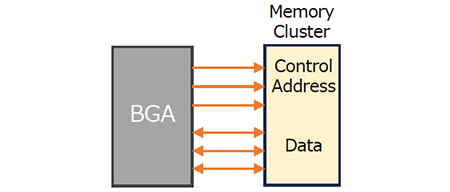

(7) メモリクラスタテスト

メモリデバイスに対してリード/ライトを行い、メモリ間の結線をテスト

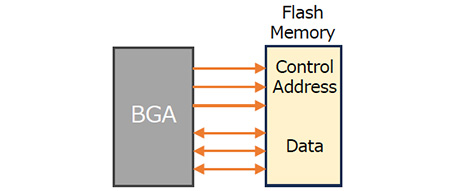

(8) フラッシュテスト

Flashメモリに対してリード/ライトを行い、Flashメモリ間の結線をテスト

検査内容の詳細・最新情報に関しては、JTAGツールベンダーにご確認ください。

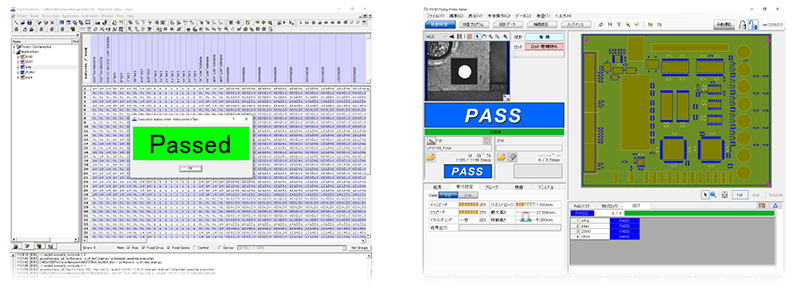

高い品質の接続保証を効率良く実現

JTAGテストとフライングプローブテスタの相互補完が、信頼性が高い通電による接続保証を高効率で高品質に実現します。

リード浮き検査手法と一般的な検出能力

オンボードプログラミングも可能

バウンダリスキャンバスを介してOBP(On BoardPrograming)も可能になります。

Flashメモリ、シリアルROM書き込みの他、PLD/FPGAの書き込みにも対応。高効率検査と併せて生産工程にも活用できます。

使用機器

フライングプローブテスタ FA1240-61, FA1240-63

JTAG Technologies社 JTAGバウンダリスキャンテスタ JTAG ProVision