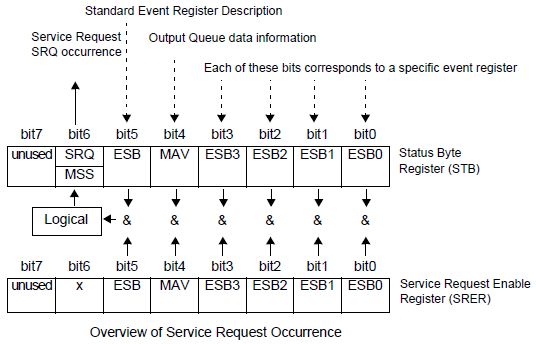

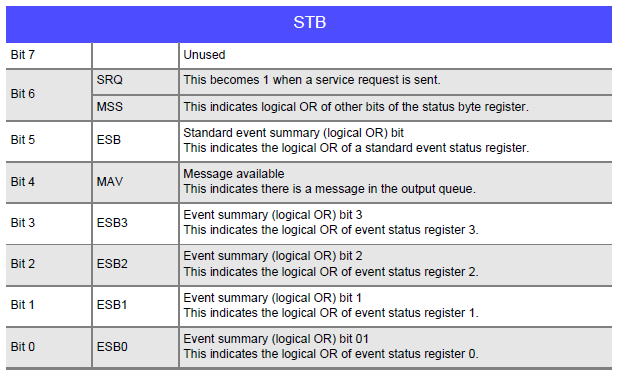

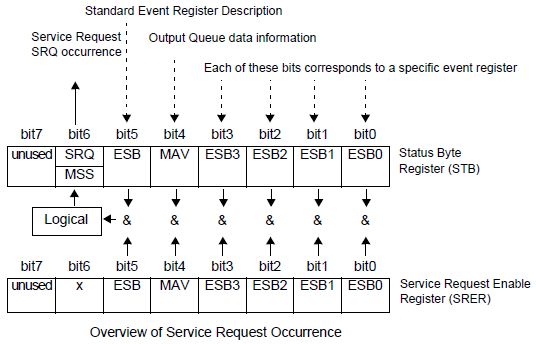

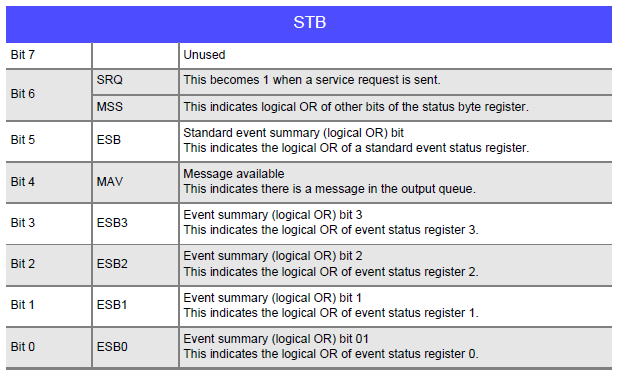

The Status Byte Register contains information about the event registers and the output queue.

Required items are selected from this information by masking with the Service Request Enable Register.

When any bit selected by the mask is set, bit 6 (MSS; the Master Summary Status) of the Status Byte Register is also set, which generates an SRQ (Service Request) message and dispatches a service request.

For RS-232C, USB and LAN bit 4 (MAV message available) of the status byte register is not set.

A status byte register is an 8-bit register output from the unit to the controller during serial polling.

If even one of the status byte register bits enabled by the service request enable register changes from "0" to "1," the MSS bit becomes 1.

At the same time, the SRQ bit also becomes "1" and a service request is generated.

The SRQ bit is always synchronized with the service request and only read and simultaneously cleared upon being serial polled.

The MSS bit is only read by an "*STB?" query and is not cleared until the event is cleared by a command such as a "*CLS" command.

When the service request enable register is used to set each of the bits to "1"the corresponding bits are enabled in the status byte register.